芯片設計是每個國家的發展重點之一,擴大中國芯片設計產業將有助於減少我國對外國芯片的依賴。 在先前的文章中,編輯者曾經介紹過芯片設計的正向和反向流程以及芯片設計的前景。 在本文中,編輯人員將向您介紹實際的芯片設計章節-RFID芯片設計中時鍾樹功耗的優化和實現。

1概述

UHF RFID是UHF射頻識別標籤芯片。 該芯片採用無源供電模式:接收到載波能量後,RF前端單元生成Vdd電源信號,以為整個芯片供電。 由於電源系統的限制,芯片無法產生大電流驅動,因此低功耗設計已成為芯片開發過程中的重大突破。 為了使數字電路部分產生盡可能少的功耗,在數字邏輯電路設計過程中,除了簡化系統結構(功能簡單,僅包含編碼模塊,解碼模塊,隨機數生成模塊,時鐘,復位模塊,存儲器控制單元以及總體控制模塊),某些電路的設計中採用了異步電路設計。 在此過程中,我們看到,由於時鍾樹消耗了數字邏輯功耗的大部分(約30%或更多),因此降低時鍾樹的功耗也已降低了時鐘邏輯電路的功耗。數字邏輯和整個標籤芯片的功能。 消費的重要一步。

2芯片功率組成和降低功耗的方法

2.1功耗構成

![]()

圖1芯片功耗構成

動態功耗主要包括短路功耗和翻轉功耗,這是該設計功耗的主要組成部分。 短路功耗是內部功耗,它是由設備中的某個時刻打開P管和N管導致的瞬時短路引起的。 周轉功耗是由CMOS器件輸出處的負載電容的充電和放電引起的。 洩漏功耗主要包括亞閾值洩漏和柵極洩漏引起的功耗。

如今,兩個最重要的功耗來源是:電容轉換和亞閾值洩漏。

2.2降低功耗的主要方法

![]()

圖2降低芯片功耗的主要方法

2.2.1降低電源電壓Vdd

電壓島:不同的模塊使用不同的電源電壓。

多路電壓等級縮放:同一模塊中有多個電壓源。 根據不同的應用在這些電壓源之間切換。

動態電壓頻率縮放:“多級電壓調整”的升級版本,可根據每個模塊的工作頻率動態調整電壓。

自適應電壓縮放:DVFS的升級版,它使用反饋電路,該反饋電路可以監視電路行為以自適應地調整電壓。

亞閾值電路(設計難度更大,仍然處於學術研究範圍之內)

2.2.2降低頻率f和周轉率A

代碼優化(提取公共因素,資源重用,操作數隔離,減少峰值功耗的串行工作等)

門控時鐘

多時鐘策略

2.2.3減小負載電容(CL)和晶體管尺寸(Wmos)

減少順序單位

芯片面積和縮小規模

流程升級

2.2.4降低漏電流Ileak

控制閾值電壓(閾值電壓)(如果使用MTCMOS,VTCMOS,DTCMOS,則閾值電壓↑漏電流↓)

控制柵極電壓(柵極電壓)(通過控制柵極-源極電壓來控制洩漏電流)

晶體管堆棧(串聯連接冗餘晶體管,增加電阻以減少洩漏電流)

門控電源(電源控製或PSO)(當模塊不工作時,請關閉電源以有效減少洩漏電流)

3 RFID芯片中時鍾樹功耗的優化

當芯片工作時,功耗的很大一部分歸因於時鐘網絡的周轉。 如果時鐘網絡很大,則由該部分引起的功率損耗將非常大。 在許多低功耗技術中,門控時鐘對翻轉功耗和內部功耗的抑製作用最強。 在該設計中,多級門控時鐘技術與特殊的時鍾樹優化策略的結合節省了大部分功耗。 該項目在邏輯設計中使用了多種優化功耗策略,並在後端綜合和物理設計中嘗試了一些方法。 通過前端和後端的幾次功耗優化和迭代,發現了邏輯代碼設計和最低功耗。

4.1在RTL階段手動添加時鐘門控

![]()

圖3門控時鐘示意圖

模塊data_reg(En,Data,clk,out)

輸入En,clk;

輸入[7:0]數據;

輸出[7:0] out;

總是@(posedge clk)

如果(En)out =數據;

endmodule

該階段的目的主要有兩個方面:首先是根據每個模塊的時鐘翻轉概率增加一個門控時鐘單元來控制翻轉率並更合理地降低動態功耗。 第二是盡可能地製造出具有平衡結構的時鐘網絡。 可以保證可以在後端時鍾樹的綜合階段添加一些時鐘緩衝器,以降低功耗。 鑄造單元庫中的ICG(集成門控)單元可以直接用於實際的代碼設計中。

4.2處於綜合階段的工具被插入到集成門中

![]()

圖4邏輯綜合期間的門控時鐘插入

#設置時鐘選通選項,max_fanout默認為無限制

set_clock_gating_style -sequential_cell鎖存器\

-positive_edge_logic {綜合} \

-control_point之前的\

-控制信號掃描啟用

#通過插入“始終啟用” ICG創建更平衡的時鍾樹

將power_cg_all_registers設置為true

將power_remove_redundant_clock_gates設置為true

read_db 設計.gtech.db

current_design頂部

鏈接

源文件design.cstr.tcl

#插入時鐘門控

插入時鐘門控

編

#生成有關插入的時鐘門控的報告

報告時鐘門控

此階段的目的是使用集成工具(DC)自動插入門控單元,以進一步降低功耗。

應該注意的是,用於插入ICG的參數設置,例如最大扇出(扇出越大,節能越多,扇出越平衡,取決於設計,如圖所示,偏斜越小),另外,還需要為更複雜的柵極控制結構插入一個常開的ICG,以使時鐘網絡結構更平衡。

4.3在時鍾樹的綜合階段優化功耗

![]()

圖5兩種時鍾樹結構的比較(a):多層深度類型; (b):少層次平板式

首先介紹時鍾樹綜合參數對時鍾樹結構的影響:

偏差:時鐘偏差,時鍾樹的總體目標。

插入延遲(延遲):時鐘路徑的總延遲,用於限制時鍾樹級別數的增加。

最大延遲:最大轉換時間限制了第一級緩衝區可以驅動的緩衝區數量。

最大電容最大扇出:最大負載電容和最大扇出限制了第一級緩衝器可以驅動的緩衝器數量。

一般設計中時鍾樹綜合的最終目標是減少時鐘偏斜。 增加級別數並減少每個扇出級別將投資更多的緩衝區,更準確地平衡每個時鐘路徑的延遲以獲得較小的偏斜。 但是對於低功耗設計,特別是時鐘頻率較低時,時序要求不是很高,因此希望可以減小時鍾樹的規模,以減少由時鍾樹引起的動態開關功耗。 如圖所示,通過減少時鍾樹的級別數並增加扇出,可以有效地減小時鍾樹的大小。 但是,由於減少了緩衝區的數量,因此,與多級時鍾樹相比,具有較少級別的時鍾樹可以大致平衡每個時鐘路徑的延遲,並產生較大的偏差。 可以看出,以減小時鍾樹的規模為目標,低功耗時鍾樹的合成是以增加一定的偏斜為代價的。

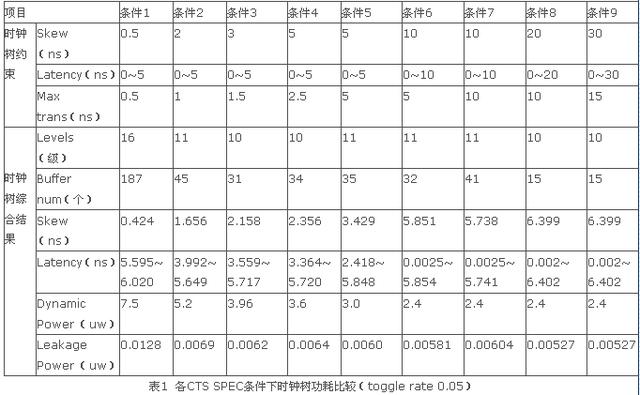

專門針對該RFID芯片,我們採用台積電0.18um CMOS LOGIC / MS / RF工藝,時鐘頻率僅為1.92M,非常低。 此時,當時鐘用於時鍾樹合成時,低時鐘用於減小時鍾樹的規模。 功耗時鍾樹綜合主要設置偏斜,等待時間和傳輸的約束。 由於限制扇出將增加時鍾樹級別的數量並增加功耗,因此未設置此值。 庫中的默認值。 實際上,我們使用了9種不同的時鍾樹約束,這些約束和綜合結果如表1所示。

![]()

5結論

如表1所示,總體趨勢是目標偏斜越大,最終時鍾樹大小越小,時鍾樹緩衝區的數量越少,相應的動態和靜態功耗也越小。 這將保存時鍾樹。 消費的目的。 可以看出,當目標偏差大於10ns時,功耗基本不變,但是較大的偏差值將導致保持時序的惡化,並在修復時序時增加插入的緩衝區數量,因此應該妥協。 從圖表中,策略5和策略6是首選解決方案。 此外,當選擇最佳偏斜設置時,您還可以看到最大過渡值越大,最終功耗越低。 這可以理解為時鐘信號轉換時間越長,所需的能量越小。 另外,可以最大程度地擴大等待時間約束的設置,並且其值對最終功耗結果影響很小。

我們的其他產品: